ニュース

AMD,TFE 2010で次世代RadeonとFusion APUの実働デモを公開。次期ハイエンドCPU情報のアップデートも

次世代Radeonを紹介するMatt Skynner氏(Corporate Vice President and GM, AMD Graphics Division, AMD) |

「Northern Islands」はカウントダウン状態

専用に作られたテクノロジーデモも公開

TFE 2010で基調講演に立ったMatt Skynner副社長は,登壇するなり,「次世代GPUの“Northern Islands”を今週金曜日に正式発表する」と予告。冒頭のプレゼンテーションでは,新たに「AMD Radeon」を名乗ることになる新製品のうち,「Radeon HD 6850」と書かれたグラフィックスカードの写真も公開されたほか,リファレンスカードも披露されている。

オープニングキーノートを担当したMatt Skynner副社長は,そのスピーチの冒頭に今週金曜日にNorthern Islandsを正式発表することを表明。スライドには「RADEON HD 6850」の写真も…… |

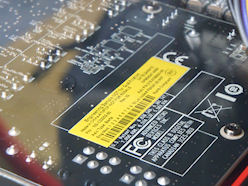

基調講演で披露されたNorthern Islands搭載カードには,「Barts」と書かれたシールが貼られていた |

エキシビション会場には,同GPUを搭載したグラフィックスカードを使ったと思われるデモも多数あり,そのデモ機に搭載されていたカードからは,金曜日(=22日)に発表されるシリーズ最初のGPUが,開発コードネーム「Barts」(バーツ:開発コードネーム)ベースであることも窺えた。

Skynner副社長のキーノートでは,このNorthern Islandsを使ったデモ「Mecha Rampage」も公開された。ATI Radeon HD 5800シリーズの発表時に「オブジェクトごとに独立した半透明化処理を施すOrder-Independent Transparency(オーダーインディペンデント・トランスペアレンシー)のデモ」として,「Mech」が披露されたのを憶えている読者も多いと思われるが,今回のMecha Rampageは,そのときのMechを主人公にしたゲーム風のものとなっている。

Northern Islandsのアーキテクチャ開発にも携わった,AMDのEric Demers副社長兼CTOは,「これまでのテクノロジーデモとは異なり,ゲーム開発現場で広く使われている(Autodesk製開発スイート)『Maya』によって,2000を超える複雑な光源処理やテッセレーションを多用した緻密な街の再現を行える。また,オープンソースの物理エンジン『Bullet Physics』によって,ゲーム物理演算を使った高速道路の破壊などが簡単にゲームで実装できるようになる」とアピール。このDirectX 11ゲーム開発環境を広く提供する意向を示し,DirectX 11ゲーム開発環境でも業界をリードしていく姿勢を見せた。

|

|

Skynner氏によれば,同社のグラフィックスチップは,今年第2四半期には単体GPUのマーケットシェアで51%を占め,DirectX 11グラフィックスのみのマーケットシェアなら90%を占める圧倒的な強さを誇っているとのこと。第2世代のDirectX 11 GPUシリーズたるNorthern Islandsへの移行を加速することで,ATI Radeon HD 5000シリーズで得たアドバンテージを保ちたい考えのようだ。

|

|

TFEの主役に躍り出るFusion APU

DirectComputeによる「Llano」実働デモも

|

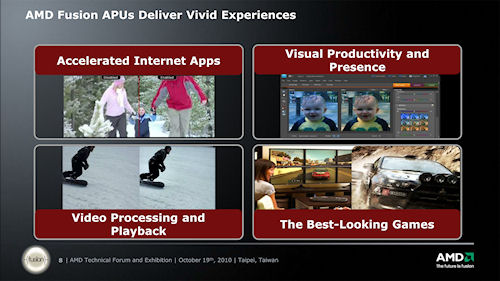

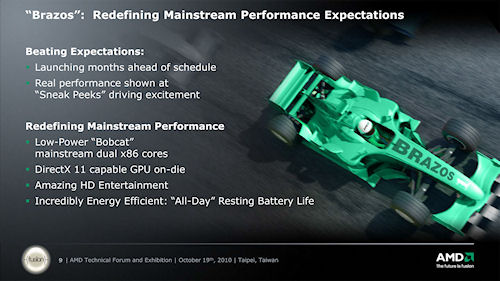

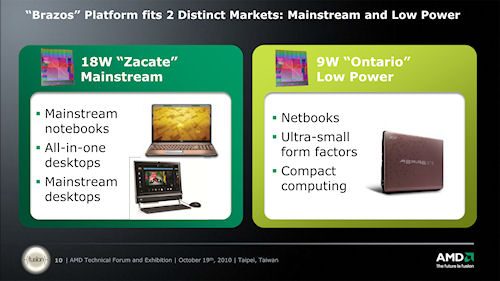

Skynner氏に続いてキーノートに登壇した,クライアント向けCPUなどを統括するChris Cloran副社長兼ジェネラルマネージャーは,APUを「顔認識やイメージ検索,ナチュラルユーザーインタフェースなどの新しいユーザー体験をメインストリーム製品にももたらすことができる,真の次世代プロセッサだ」と紹介。そのうえで,今年9月のIntel Developers Forum 2010 San Fransicoにあわせて報道関係者へ公開された「Zacate」(ザカテ:開発コードネーム)と,その低消費電力版となる「Ontario」(オンタリオ,同)のプラットフォーム「Brazos」(ブラゾス)では,DirectX 11世代のGPUが持つ強力な汎用コンピューティング能力や,高解像度ビデオ再生支援機能であるUVDを効率よく活用することで,システムレベルの消費電力を低減でき,1日中のバッテリー駆動が可能なノートPCが実現可能と説明する。

その最新デモとしてCloran氏は,「Core i5-520M/2.40GHz」搭載システムとZacateのリファレンスキットによるN-Body演算性能の比較を披露。IntelのノートPCと比べて,システム全体の消費電力を半分に抑えつつ,約3倍の浮動小数点演算性能を発揮するとアピールした。

この比較で用いられたのは,DirectX 11 SDKに収められている「NBodyGravityCS11」。Zacateシステムでは,演算処理をGPUコアが行うため,CPU負荷が6〜9%しかかからないのに対し,Core i5ではCPUによる処理となるため,CPU負荷が100%に貼り付いていた。

APUでは,GPUが負荷を受け持つことで消費電力が下がる可能性を示唆しつつも,CPU単独で処理するには“重すぎる”アプリケーションが,APUの持つ汎用コンピューティング性能により,エントリークラスのPCでも動作させられるようになる可能性が感じられるデモだと言えるだろう。

|

|

|

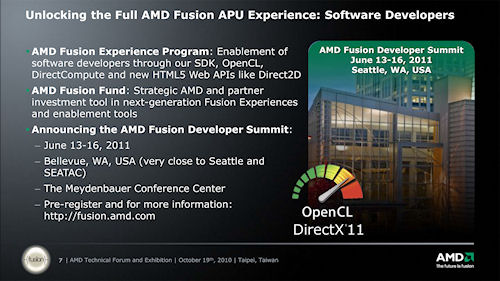

なおAMDは,2011年6月に,米シアトル市で,「AMD Fusion Developer Summit」を開催し,OpenCLやDirectCompute,DirectX 11を活用したAPUに最適なソフトウェアの開発を加速させる意向も表明している。

|

さて,Cloran氏はここで,来年半ばに市場投入予定の次世代APU「Llano」(ラノ,開発コードネーム)のウェハを公開するとともに,テクノロジーデモも披露した。デモは,Zacateのデモと同じN-Body演算と,3200万桁までの円周率計算,Blu-ray Discの1080pビデオ再生を同時に行い,基本性能の高さをアピールするというものだ。

ここで注目したいのがN-Body演算の速度で,上述したZacateのデモが21.83GFLOPSであるのに対し,こちらは30GFLOPS以上の数値を達成しており,LlanoのGPUの性能がZacateより高いことを示唆している。

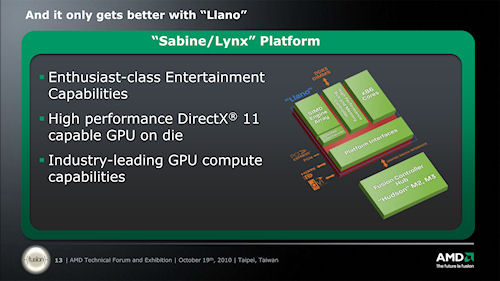

Llanoは,GLOBALFOUNDRIESの32nm SOIプロセスを採用し,最大4つのCPUコアを統合するAPUだが,下位モデルとなるZacateやOntarioよりも強力なグラフィックス機能を実装することも明らかにされた。また,Llanoのプラットフォームとしては,デスクトップ向けの「Lynx」(リンクス)と,モバイル製品向けの「Sabine」(サビーネ),計2種類が用意され,チップセットには開発コードネーム「Hudson M2」(ハドソンM2)および「Hudson M3」が用意されることも明らかになっている。

|

ゲーマー待望の新CPUアーキテクチャー

Bulldozer搭載製品は2011年内登場か

ゲーマーにとって最も気になるデスクトップPC向けの次期ハイエンドCPUに関しても,TFE 2010ではアップデートがあった。

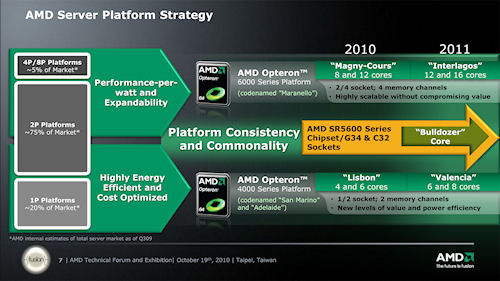

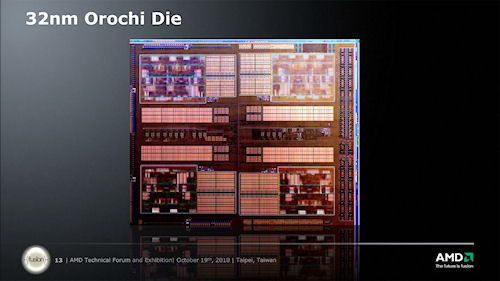

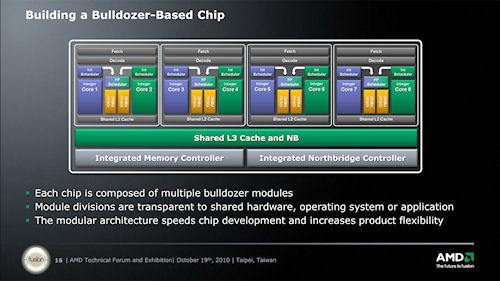

AMDでサーバー製品を統括するDon Newell上級副社長兼CTOは,高性能CPU向けの次世代アーキテクチャ「Bulldozer」(ブルドーザ,開発コードネーム)を採用するサーバー&ワークステーション向けCPU「Interlagos」(インテルラゴス,同)と「Valencia」(ヴァレンシア,同),そしてデスクトップPC向けの派生品となる「Zambezi」(ザンベジ,同)を,いずれも2011年内に市場投入する意向を表明。また,AMDで半導体プロセスや回路技術を担当するJean Boufarhat副社長のキーノートでは,従来のCPUコアにあたる「Bulldozer Module」を4つ搭載した半導体デザイン「Orochi」(オロチ)のダイ写真も公開された。

|

Orochiは,もともとBulldozerアーキテクチャを採用する最初のCPUコードネームとされていたもので,現在そのコードネームは,ValenciaとZambezi共通の半導体デザイン(=ダイ)を指すものとされているようだ。

|

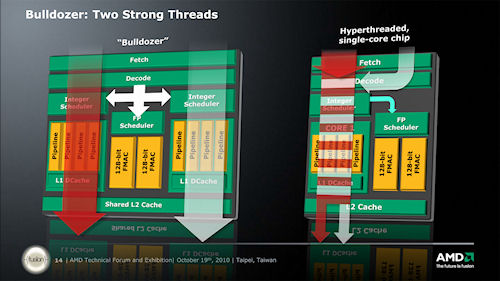

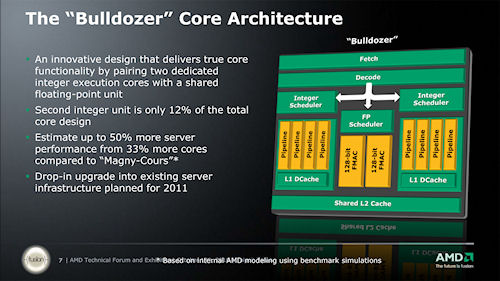

このOrochiのダイ写真を見ると,AMDのCPUロードマップにあるBulldozer世代の「コア数」は,1 Bulldozer Module=2 CPUコアとして計算されていることが分かる。Bulldozerコアアーキテクチャは,1つのコアに2基の整数演算コアを統合することで,CPUコア2基分の整数演算処理能力を実現(※浮動小数点演算コアは共有する)。しかも,「2つめの整数演算コアを追加しても,現行のコアデザインに比べ12%しか半導体サイズは大きくならない」(Boufarhat副社長)。

このBulldozer Moduleの採用により,16コア(8 Bulldozer Module)のInterlagosでは,12コアを統合したMagny-CoursコアのOpteron 6000シリーズよりも50%高いサーバー処理性能を,約3割増のCPUコアで実現できるとして,消費電力あたりのパフォーマンスでも大きなアドバンテージがあるとアピールする。

|

|

|

このようにAMDは,2011年に控えるAPUへの移行に向けた本格的な動きを加速させるとともに,BobcatとBulldozerという,2つの新しいx86 CPUアーキテクチャを投入することを,TFE 2010でコミットした格好だ。

なお,これらの計画については,さらに新情報が入り次第お伝えする予定だ。

- 関連タイトル:

Radeon HD 6800

Radeon HD 6800 - 関連タイトル:

AMD FX(Zambezi)

AMD FX(Zambezi) - 関連タイトル:

AMD E-Series,AMD C-Series

AMD E-Series,AMD C-Series - 関連タイトル:

AMD A-Series(Llano)

AMD A-Series(Llano) - この記事のURL:

キーワード

- ニュース

- イベント

- HARDWARE:Radeon HD 6800

- HARDWARE

- GPU

- AMD

- Radeon

- HARDWARE:AMD FX(Zambezi)

- HARDWARE:AMD E-Series,AMD C-Series

- CPU

- ライター:本間 文

- HARDWARE:AMD A-Series(Llano)

(C)2010 Advanced Micro Devices, Inc.

(C)2011 Advanced Micro Devices, Inc.