ニュース

Intelの3次元実装技術「Foveros」で,10nm CPUと次世代GPU,DRAMを1パッケージ上で積み重ねることが可能に

|

記事化を前提とした会ではなかったので,内容は多岐にわたったうえにとりとめのない話も多かったのだが,いくつか4Gamer読者にも興味深そうな話題があったので,ポイントになるものを簡単に紹介しよう。

Foverosは機能ごとに最適なプロセスで実装してパッケージングを可能に

最初に取り上げる話題は,Intelの3次元積層技術「Foveros」(フォベロスまたはファベラス)である。ただ,Foverosについて説明するには,プロセッサの実装技術について簡単に説明しておく必要があるだろう。

|

とはいえ,求められる機能や性能,価格帯によっては,1つのダイにまとめるのが難しいことは今でもある。分かりやすいのがGPUで,AMDやNVIDIAが展開するミドルクラス以上のGPUを,x86 CPUと同じダイに実装した製品はない。AMDは,Zen世代のCPUにVega世代のGPUコアを統合したAPU製品を展開しているが,搭載するGPUコアの規模は,単体GPUに比べると6分の1以下である。

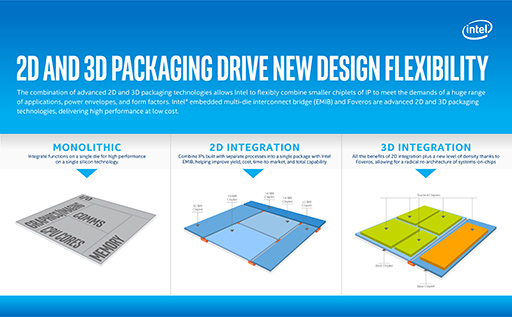

単一のダイに異なる機能を実装する技術に対して,複数のダイを1つのパッケージ上に実装する「Multi-Chip Module」(MCM)と呼ばれる技術もあり,これもさまざまな製品で利用されている。

たとえば,Intelの薄型ノートPC向けCPUでは,GPUやI/Oを含むCPUのダイと,チップセット機能(プラットフォームI/O,以下 PCH)を1つのパッケージ上に実装した製品が主流だ。また,Intelは,パッケージ上でダイ同士を接続するインターコネクト技術「Embedded Multi-Die Interconnect Bridge」(EMIB)を開発。EMIBを用いてIntel製CPUとAMD製GPU,およびグラフィックスメモリを1パッケージに収めた「Core Mobile Processor with Radeon RX Vega M Graphics」(開発コードネーム「Kaby Lake-G」,以下 コードネーム表記)を2017年にリリースしている。

|

|

|

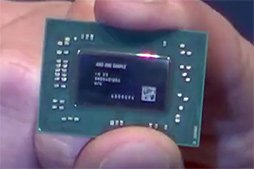

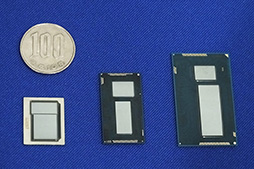

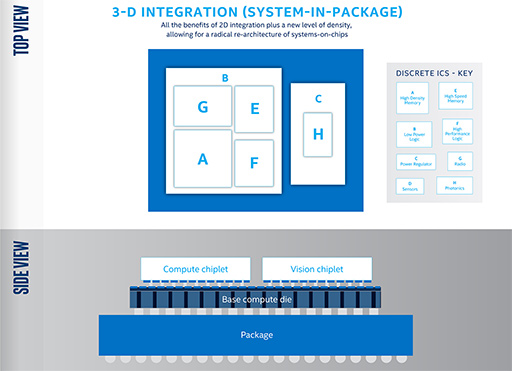

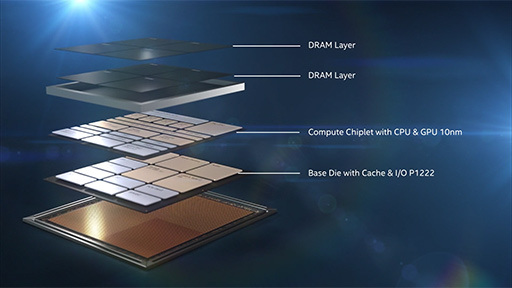

ずいぶんと前置きが長くなったが,ここからがようやくFoverosの話である。IntelはEMIBの発展系として,メモリダイだけでなくCPUやGPU,I/OコントローラやAI処理プロセッサ,SRAMや電源回路といった多彩な機能を立体的に実装する技術を開発した。これがFoverosである。Foverosを用いると,1パッケージ上にメモリだけでなく,異なる機能ブロックを積み重ねて実装することが可能になるのだ。

|

土岐氏はFoverosの利点について,異なる機能を1パッケージにまとめつつ,性能や消費電力,コスト面のメリットがあることを挙げた。単一のダイに複数の機能を組み込む場合,すべての機能は同じプロセスで製造することになる。しかし土岐氏は,デバイスによってその時点で最適なプロセスは異なる場合があると言う。CPUやGPUと,モデム機能やSRAMは別々のプロセスを用いたほうが,同じプロセスになる単一ダイよりも消費電力やコスト面で理に適う場合もあるというわけだ。

単一のダイに複数の機能を盛り込もうとすると,必然的にダイサイズが大きくなって製造の難度や製品のコストが上がってしまう。しかし,複数のダイに分けて機能を実装して,それを立体的に積み重ねて1パッケージにできるのであれば,1つ1つのダイサイズは小さくできるので,難度やコストの問題を緩和できる理屈だ。

|

また土岐氏は,Foverosで積み重ねるダイは,すべてをIntelが製造する必要がないというのも利点になると述べている。AMDやNVIDIAのGPUが使うHBMを,ほかのメモリチップメーカーが製造しているのと同じことだろう。

それに加えて,開発,あるいは製造時における各機能のテストがしやすくなるのも利点であろうと土岐氏は述べた。単一ダイに複数の機能を盛り込むと,特定の機能ブロックだけをテストするのは難しいそうだ。問題が発生したときは,ダイ全体が使い物にならなくなる場合もある。その点,複数ダイに機能を分けておけば,理論上はテストがしやすくなるし,問題発生時の交換もしやすくなるだろうと,土岐氏は説明していた。

ただ土岐氏は,Foverosにも解決すべき課題があると指摘する。課題の1つはコストだが,もう1つ大きな問題が発熱だ。異なるプロセスで作られた異なる機能を持つダイは,それぞれ発熱の仕方も変わる。しかもFoverosは,PCのように高性能なシステムでの利用を想定しているので,各機能も高い性能を要求されるはずだ。それらを積み重ねて動作させても,熱による問題が発生しないようにするのが難しいことであろうことは,専門家ではない筆者にも理解できる。

Intelでは,Foverosを採用した製品として,開発コードネーム「Lakefield」を2019年後半に投入する予定であるという。Lakefieldは,22nmプロセスで製造するI/Oおよびキャッシュのダイ上に,10nmプロセスの次世代CPUマイクロアーキテクチャ「Sunny Cove」による高性能CPUと,4コアのAtomプロセッサ,および第11世代の統合型グラフィックス機能からなるダイを載せて,さらにその上にはDRAMのダイを積み重ねる予定であるそうだ。

|

M.2 SSD上にOptane Memoryを組み合わせたOptane memory H10

話はまったく変わって,次はIntelが力を入れているOptane Memoryの話題だ。

IntelがMicron Technology(以下,Micron)と協同で開発したメモリ技術「3D XPoint」(3Dクロスポイント)を発表したのは2015年のこと。「既存のNAND型フラッシュメモリよりも1000倍高速で,1000倍の寿命があり,しかも10倍のセル密度を実現できる」という触れ込みで登場した革新的技術だ。

PC分野では,高速ディスクキャッシュとして利用できるPCI Express(以下,PCIe)接続のM.2型Optane Memoryや,Optane MemoryベースのSSD製品(関連記事)が流通しているので,メジャーというほどではないものの,PCに詳しい人なら知っているものだろう。

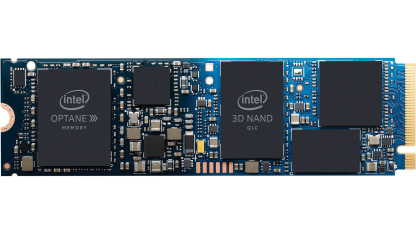

Intelは2019年春に,Optane Memoryを使った新しい製品を投入する。それは「Optane memory H10」というストレージで,PCIe接続のM.2カード上に,容量未公開のOptane MemoryとIntel製3D NANDフラッシュメモリを使った容量1TBのSSDを混載するというものだ。

|

Optane memory H10については,詳しいスペックがまだ明らかになっていないので,Optane Memory部分の容量がどの程度になるのかや,キャッシュではなくストレージとして使えるのか,あるいは混載しているSSD以外のストレージに対してもキャッシュとして利用できるのかといった点は不明である。

これについて土岐氏は,ストレージ用のドライバソフト側で,Optane Memoryの使い方を設定できるようになる予定と述べていた。Optane Memory部分を,3D NANDにおける性能面の弱点を補う用途に使えると,ちょっと面白いかもしれない。

次世代CPU「Ice Lake」ではグラフィックスドライバにも力を入れる

Intelは2019年前半に,開発コードネーム「Ice Lake」と呼ばれる次世代CPUを市場に投入予定だ。Ice Lakeは,Sunny CoveマイクロアーキテクチャのCPUコアと,第11世代の統合型グラフィックス機能(以下,統合型GPU)を実装するという。

Intelによると,第11世代の統合型GPUは1TFLOPSの演算性能を有するとのこと。単体GPUの演算性能が1TFLOPSに達したのは,2008年に登場した「Radeon HD 4850」でのことなので,それに比べると11年遅れ。2013年発売のPlayStation 4の場合,内蔵GPUは1.84TFLOPSの性能を有することを考えると,「これ1つでどんなゲームも快適」とまではいかない。とはいえ,統合型GPUでも快適にプレイ可能なゲームが増えること自体は,ゲーマーにとって歓迎すべきことだろう。

|

ソフトウェア面での改善で,統合型GPUのグラフィックス性能を向上させる余地は大いにあるので,今までは十分でなかったドライバソフトの最適化を頑張ってやっていくとKoduri氏は強調しているとのこと。実際にその成果が見られるのは,Ice Lakeが登場したうえで,ドライバソフトのリリースが進んでからの話になるが,Intelがグラフィックス性能におけるドライバソフトの重要性に目を向けているというのは,喜ばしい話題と言えるだろう。

- 関連タイトル:

第10世代Core(Ice Lake,Comet Lake)

第10世代Core(Ice Lake,Comet Lake) - この記事のURL: